Bật mí CPU thế hệ mới AMD Milan (Zen 3) và Genova (Zen 4)

Tại hội nghị HPC-AI Advisory Council UK, AMD đã tiết lộ chi tiết mới về kiến trúc Zen 3 và Zen 4 của mình. Cùng với một lộ trình đưa ra cho chúng tôi dòng thời gian ra mắt và một số thông số kỹ thuật chính cho các dòng EPYC Milan và Genova, thế hệ tiếp theo của dòng vi xử lý trung tâm dữ liệu EPYC. Bài thuyết trình đã được tải lên YouTube và sau đó được đưa xuống một cách khá nhanh chóng, có thể là do công ty chưa sẵn sàng tiết lộ những chi tiết quan trọng này. Chúng tôi đã lấy một bản sao của video trước khi nó bị gỡ xuống và có một số chi tiết mới về kế hoạch tương lai của AMD.

Kiến trúc vi mô Zen mang tính cách mạng của AMD đã giới thiệu với thế giới các bộ xử lý dựa trên chiplet được sản xuất hàng loạt cho phép công ty sử dụng cùng một thiết kế cơ bản trên cả chip dành cho người tiêu dùng chính và doanh nghiệp. Mọi thay đổi đối với kiến trúc sẽ lọc ra tất cả các chip cho người dùng chính và doanh nghiệp mới của công ty, có nghĩa là những thay đổi này có thể sẽ áp dụng với dòng chip Ryzen trong tương lai.

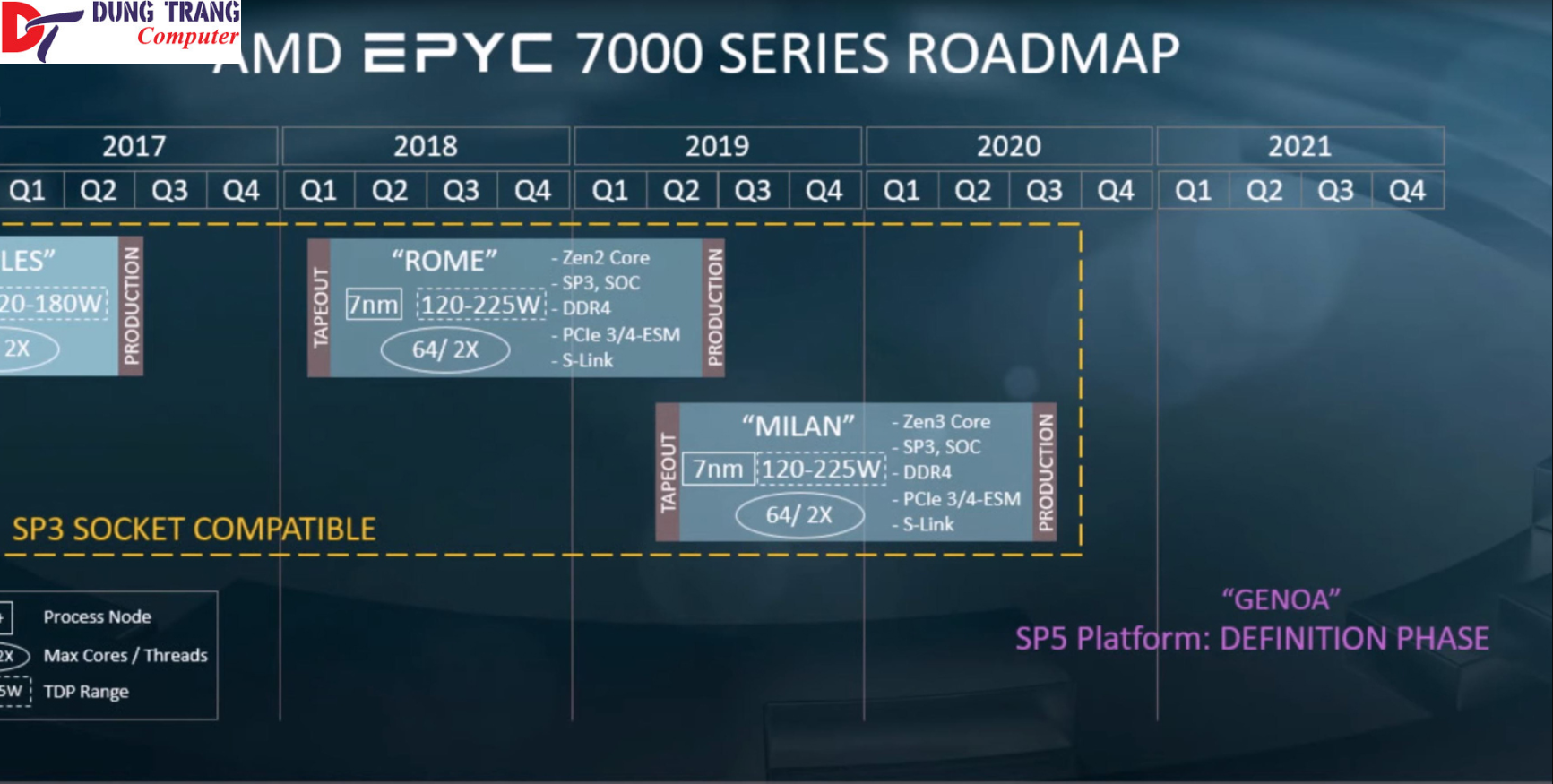

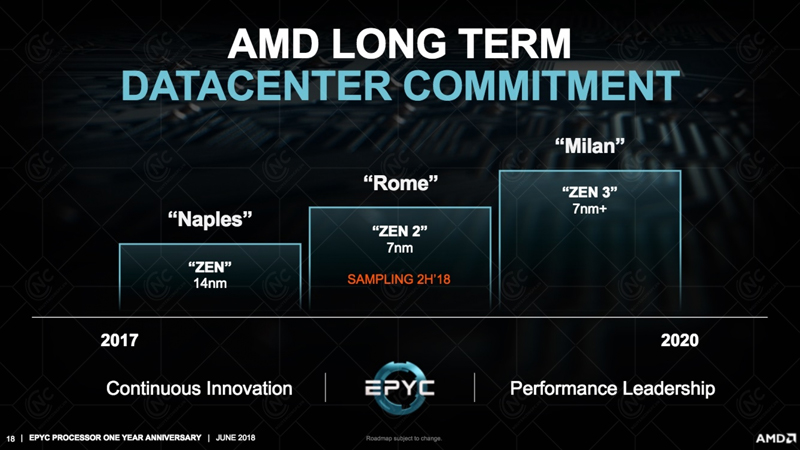

Nhưng khi AMD đã đưa ra một lộ trình phác thảo sự xuất hiện của chip Milan, có lõi Zen 3, đi vào sản xuất vào quý 3 năm 2020. Điều đó có nghĩa là AMD đang thực hiện kế hoạch cung cấp các bản cập nhật hàng năm cho kiến trúc của mình. AMD cũng lưu ý rằng họ đã loại bỏ các con chip và đang lấy mẫu chúng cho khách hàng.

Các chip Milan mới sẽ có tiến trình 7nm +, phiên bản được làm mới của tiến trình hiện tại với hiệu suất cao hơn. Chúng cũng có tối đa 64 lõi giống như các mẫu Rome thế hệ hiện tại và socket SP3, nghĩa là chúng tương thích ngược với các nền tảng hiện có. Họ cũng sẽ hỗ trợ tương tự cho tám kênh DDR4 và PCIe 4.0 và TDP cơ bản 120-225W, mặc dù điều này hợp lý để mong đợi các biến thể TDP cao hơn như 7H12 cũng đang hoạt động. Các chip này cũng có hai luồng trên mỗi lõi, làm im lặng những tin đồn khá mơ hồ rằng AMD sẽ chuyển sang bốn luồng trên mỗi lõi (SMT4).

Các chip Milan thế hệ tiếp theo vẫn có cách sắp xếp chín chiplet giống như các mẫu Rome thế hệ hiện tại, với tám chiplet tính toán và một I/O die, cùng với tám lõi được gán cho mỗi chiplet tính toán. Các thông số kỹ thuật phần lớn không thay đổi, ít nhất là trong các thông số chính, ngụ ý Milan chỉ đơn thuần là một “Tock” tương đương, hoặc chỉ là một sự chuyển sang thế hệ thứ hai của tiến trình 7nm (7nm +).

Tuy nhiên, AMD cũng tiết lộ rằng công ty đã thực hiện một sự thay đổi đáng kể đối với việc sắp xếp bộ đệm trong chip, điều này cho thấy rằng có một việc quan trọng đang được thực hiện bên trong CPU để cải thiện băng thông trên mỗi chu kỳ (IPC) và giảm độ trễ. AMD hiện đang chia các CPU của mình thành hai Tổ hợp điện toán gồm bốn lõi (CCX), mỗi bộ được trang bị bộ nhớ cache L3 16 MB. Đối với Milan, việc thay đổi thành tám lõi được kết nối với một bộ đệm L3 32 MB hợp nhất, sẽ loại bỏ một lớp độ trễ trong khuôn tính toán.

Phần lớn sự thành công của một thiết kế dựa trên khả năng cung cấp dữ liệu cho các lõi thực thi, và những cải tiến quan trọng trong các lĩnh vực này sẽ mang lại sự gia tăng IPC, giúp chúng tôi tăng hiệu suất hơn so với chúng tôi thường mong đợi từ một thế hệ làm mới đơn thuần. Kết hợp với xung nhịp được cải thiện từ một biến thể nhanh hơn của tiến trình 7nm và AMD có thể cung cấp một số mức tăng hiệu suất gen-on-gen đặc biệt, bất kể số lượng lõi vẫn không đổi.

Điều đó phản ánh sự khẳng định của AMD rằng nó sẽ tiếp tục cung cấp các mức hiệu suất mới đột phá với mỗi lần lặp lại của kiến trúc vi mô của nó, phá vỡ khuôn mẫu của các cập nhật hiệu suất gia tăng mà chúng ta đã quen thuộc trong thập kỷ thống trị của Intel. Về phía đội xanh, Intel cũng đã có kế hoạch đáp trả với chip Sapphire Rapids dự kiến ra mắt vào quý I/2021, hỗ trợ RAM DDR5 8 kênh và PCIe 5.0.