Synopsys tiết lộ giải pháp giao diện PCI Express 6.0 hoàn chỉnh.

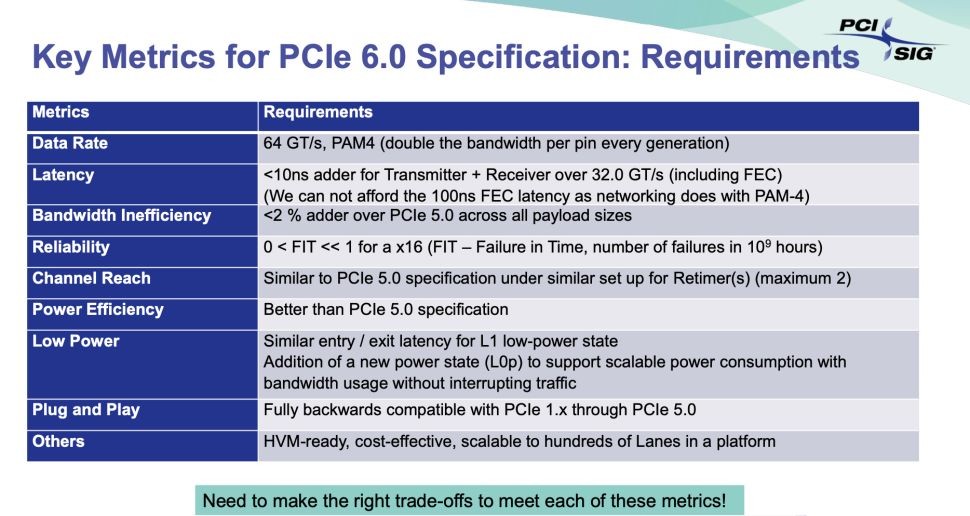

Các thông tin về thế hệ PCIe 6.0 được nhắc tới nhiều lần, thông số kĩ thuật chi tiết cuối cùng của thế hệ này vẫn còn nhiều tháng nữa mới được công bố.

Tuy nhiên, những bản dự thảo cuối cùng được phát hành cách đây khoảng năm tháng cho phép các nhà thiết kế chip và nhà phát triển IP bắt đầu triển khai công nghệ mới vào sản phẩm của họ vì không có tính năng mới nào được thêm vào hoặc sửa đổi.

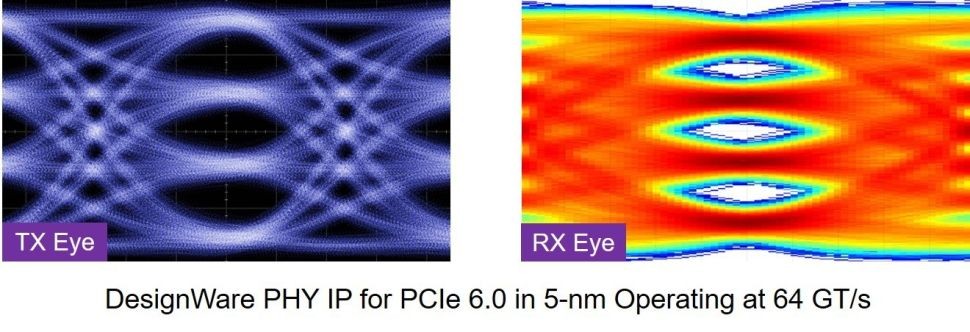

Tuần này, Synopsys đã giới thiệu giải pháp IP PCIe 6.0 hoàn chỉnh đầu tiên trong ngành cho phép các nhà sản xuất chip tích hợp giao diện mới vào thiết kế của của họ và được thực hiện dựa trên tiến trình 5 nm.

Gói DesignWare IP của Synopsys cho PCIe 6.0 bao gồm bộ điều khiển (với giao diện Synopsys hoặc tùy chọn giao diện AMBA 5/4/3 AXI của Arm’s), giao diện vật lý (PHY) và IP xác minh.

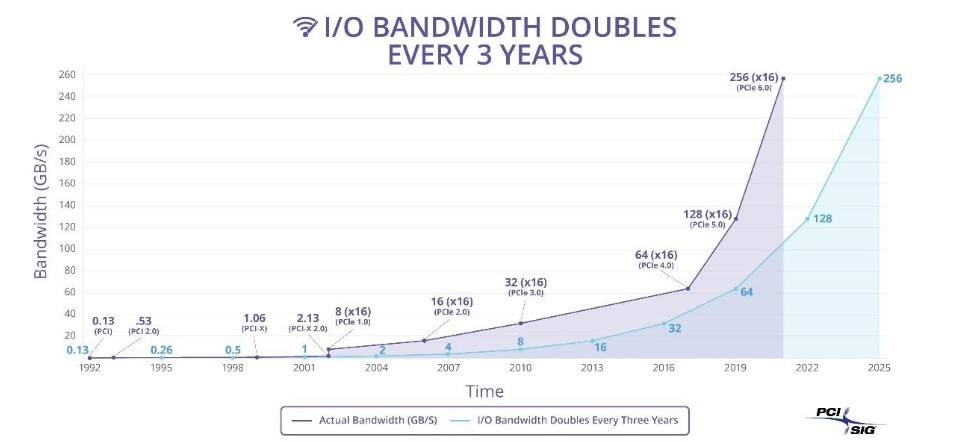

Giải pháp mà Synopsys đưa ra cho phép các nhà thiết kế chip đưa IP của bộ điều khiển và giao diện vật lý vào thiết kế trên tiến trình 5 nm của họ và sau đó xác minh rằng mọi thứ hoạt động chính xác bằng cách sử dụng IP xác minh được cung cấp. Băng thông bao nhiêu? Lên đến 128 GB / s trên giao diện x16 – theo mỗi hướng.

Điều đó có nghĩa là giải pháp PCIe 6.0 có khả năng truyền dữ liệu lên đến 256 GB / s.

Bộ điều khiển hỗ trợ đầy đủ tốc độ truyền dữ liệu lên đến 64 GT / s mỗi chân, tăng từ 32 GT / s đối với PCIe 5.0 và 16 GT / s đối với PCIe 4.0. Nó cũng hỗ trợ điều chế biên độ xung với bốn mức tín hiệu (PAM4), sửa lỗi chuyển tiếp có độ trễ thấp (FEC), chế độ FLIT và trạng thái nguồn L0p – đây là tất cả các tính năng chính và mới của PCIe 6.0.

Trên hết, bộ điều khiển DesignWare PCIe 6.0 của Synopsys cũng hỗ trợ các thuật toán DSP thích ứng riêng giúp tối ưu hóa khả năng cân bằng tương tự và kỹ thuật số để giảm thiểu 20% mức điện năng trên các giao diện chip-to-chip, riser card và bảng nối đa năng.

Synopsys nói rằng kiến trúc của bộ điều khiển PCIe 6.0 và giao diện vật lý có khả năng nhận biết vị trí để giảm thiểu nhiễu xuyên âm của các gói tin ở tốc độ truyền dữ liệu cao. Hơn nữa, công ty tuyên bố rằng họ sử dụng một đường dẫn dữ liệu được tối ưu hóa để đảm bảo độ trễ cực thấp.

John Koeter, phó chủ tịch tiếp thị cấp cao cho biết: “Các ứng dụng điện toán đám mây, lưu trữ và học máy tiên tiến đang truyền tải lượng dữ liệu đáng kể, đòi hỏi các nhà thiết kế phải kết hợp các giao diện tốc độ cao mới nhất với độ trễ tối thiểu để đáp ứng nhu cầu băng thông của các hệ thống này”, John Koeter, phó chủ tịch tiếp thị và chiến lược cho IP tại Synopsys.

“Với giải pháp DesignWare IP hoàn chỉnh của Synopsys cho PCI Express 6.0, các công ty có thể bắt đầu sớm các thiết kế dựa trên PCIe 6.0 của họ và tận dụng chuyên môn đã được chứng minh của Synopsys và vị trí dẫn đầu trong PCI Express để đẩy nhanh con đường dẫn đến thành công silicon của họ.”

Chỉ trong vòng 18 tháng qua, chúng ta đã thấy phần cứng dành cho người tiêu dùng – GPU và SSD M.2 – hỗ trợ PCIe 4.0, với việc Nvidia bổ sung hỗ trợ cho Gen4 cho dòng GPU Ampere bắt đầu từ tháng 9 năm ngoái. Chúng ta còn một khoảng thời gian trước khi PCIe 5.0 bắt đầu xuất hiện trong các card đồ họa tốt nhất và ổ SSD tốt nhất , chưa kể đến bo mạch chủ, nhưng PCI-SIG thế hệ thứ 6 về cơ bản đã hoàn thành.

Băng thông tăng lên sẽ quan trọng đến mức nào đối với khối lượng công việc lưu trữ và đồ họa? Đối với người dùng gia đình, có lẽ không nhiều.

Các giao diện tốc độ cao này chủ yếu nhắm mục tiêu đến khối lượng công việc của trung tâm dữ liệu và siêu máy tính, và có thể sẽ mất nhiều năm trước khi phần cứng của người tiêu dùng cần tốc độ như vậy.

Theo Tomhardware